MAX121與TMS320VC5402在高速數據采集中的接口

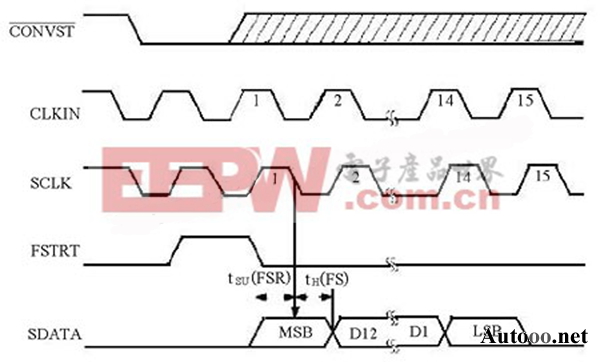

CLKIN是MAX121的輸入時鐘,而SCLK使數據移位進入處MAX121,CLKIN由外部時鐘振蕩器驅動(5MHz)。TMS320VC5402的XF引腳(通用I/O口)驅動MAX121輸入端為低,啟動一次轉換。TMS320VC5402的BCLKR0(接收時鐘)端配置為輸入,并由MAX121的SCLK輸出端驅動。MAX121的SDATA輸出端數據在時鐘的上升沿改變狀態,而在時鐘下降沿,數據被鎖存到TMS320VC5402的DR輸入端。這樣可提供1/2個時鐘周期,以滿DR輸入端所需要的數據建立和保持時間。MAX121 SCLK和SDATA之間的最大時滯在+25時為65ns,所以1/2個時鐘周期足以滿足要求的建立和保持時間,工作時序如圖6所示。

圖 6

MAX121的FSTRT輸出驅動TMS320VC5402的BFSR0輸入,以對數據分幀。FSTRT輸出的下降沿指示MSB已準備好,可被鎖存。在下一個時鐘下降沿,MSB被鎖存在TMS320VC5402。使用這種,配置TMS320VC5402可接收16位,于是14位數據被時鐘同步移入DSP,同時跟隨兩位尾隨的0。

結論

該設計部論的硬件部分和軟件部分都已經得到實驗驗證,并將其應用到研發之中,與同類A/D比較,而且有著較高的分辨率,實用性很強,與DSP等有簡易的接口,應用方便。

評論