μC/OS-III在Cortex-M3處理器上的移植

摘要:為了將μC/OS-III移植到Cortex-M3處理器上,選用RealView MDK作為軟件開發平臺,針對Cortex-M3處理器特性編寫了移植所需的C語言和匯編語言源代碼,并驗證了移植的正確性。移植后的μC/OS-III能夠穩定運行于Cortex-M3處理器上。該移植對大部分Cortex-M3處理器具有通用性,對其他架構處理器的μC/OS-III移植具有參考作用。

關鍵詞:μC/OS-III;嵌入式操作系統;ARM;Cortex-M3;移植

引言

μC/OS-III是一款基于優先級調度的搶占式實時內核,Micrium公司于2011年8月公開了μC/OS-III的源碼,其源碼遵循ANSIC標準,因而具有良好的移植性,相信其將會被移植到越來越多的處理器體系上。本文主要完成基于Cortex-M3處理器的μC/OS-III移植,通過本次移植,加深對嵌入式操作系統原理的理解。此外,在μC/OS-III移植成功的基礎上進行嵌入式應用程序開發,可以把主要精力集中到應用程序上,而硬件資源交由μC/OS-III管理,從而使得嵌入式應用程序更易開發和維護,在嵌入式軟硬件結構變得越來越復雜的今天具有現實意義。

1 μC/OS-III和Cortex-M3特點

相對以前的版本,μC/OS-III最大改進之處在于允許多個任務運行于同一優先級上,相同優先級的任務按時間片輪轉調度,內核對象的數量不受限制,以及接近于零的中斷禁用時鐘周期。

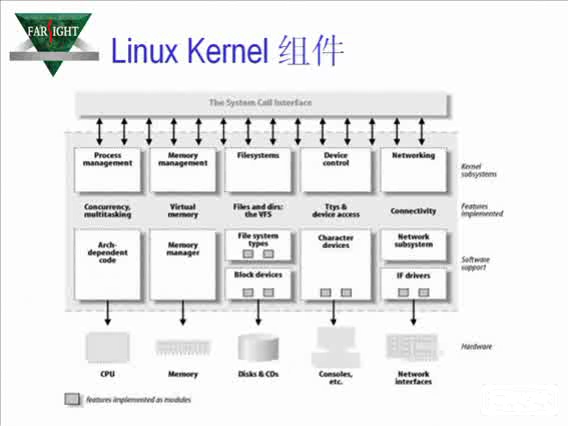

Cortex-M3是ARM公司推出的基于ARMv7-M架構的內核,主要針對高性能、低成本和低功耗的嵌入式應用。Cortex-M3擁有固定的存儲器映射,采用更高效的NVIC(Nested Vectored Interrupt Controller)、更簡單的堆棧以及更高性能的指令集,且NVIC(包括SysTick)的寄存器位置固定,極大地方便了μC/OS-III的移植及在基丁Cortex-M3內核的處理器之間的遷移。

2 移植

2.1 移植方案

本文移植μC/OS-III內核的版本為V3.02.00,其源代碼下載地址見參考文獻。選用意法半導體(ST)公司生產的基于Cortex-M3內核的STM32F103RBT6微控制器作為硬件實驗平臺,而編譯環境采用RealViewMDK V3.5。

Cortex-M3支持兩種特權級別:特權級和用戶級,μC/OS-III內核和用戶代碼都運行于特權級下。Cortex-M3還支持兩個棧指針MSP和PSP,μC/OS-III內核和ISR(Interrupt Service Routine)使用MSP,μC/OS-III的任務則使用PSP。

首先針對Conex-M3處理器的特性編寫與內核、CPU和BSP(Board Support Package)相關的源代碼,然后創建若干個簡單的用戶任務,在具體的硬件平臺上測試移植后的μC/OS-III。

2.2 內核相關

2.2.1 編寫os_cpu.h

os_cpu.h頭文件主要是對上下文切換函數和時間戳獲取函數進行宏定義。μC/OS-III的上下文切換包括兩種類型:任務級上下文切換OS_TASK_SW()和中斷級上下文切換OSIntCtxSw()。它們使用相同的代碼置位ICSR.PENDSVSET以懸起PendSV異常,由PendSV的ISR“緩期執行”上下文切換。

OS_TS_GET()的作用是獲取當前時間戳,若使能μC/OS-III的時間戳功能,則將OS_TS_GET()宏定義為CPU_TS_TmrRd(),否則簡單地宏定義為0。

2.2.2 編寫os_cpu_a.asm

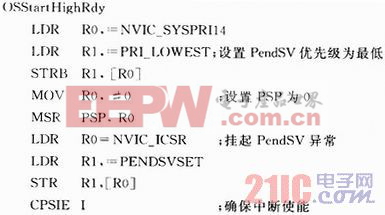

在os_cpu_a.asm文件中需要用匯編指令實現OSStartHighRdy()函數和PendSV的ISR。OSStartHighRdy()函數被內核用于調度第一個最高優先級的就緒任務,以開始多任務運行環境,匯編代碼實現如下:

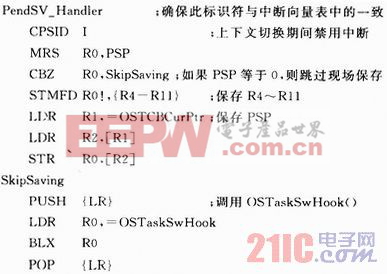

Cortex-M3支持PendSV異常,而PendSV異常的典型應用場合就是上下文切換。得益于Cortex-M3的中斷機制,μC/OS-III上下文切換只需保存和恢復R11~R4、PSP,而PSR、PC、LR、R12、R3~R0由硬件自動保存和恢復。PendSV的ISR匯編代碼如下:

評論