TD-SCDMA發射機有效提高基站效率

TD-SCDMA是頻分多址(FDMA)、時分多址(TDMA)和碼分多址(CDMA)三種技術的綜合利用。它與具有密集頻譜重用支持功能的智能天線的結合使用,可實現對無線頻譜的高效利用。

基于TD-SCDMA的系統可滿足第三代移動通信(3G)在新興的密集式應用、分組型傳輸以及移動互聯網應用方面對高數據率的要求,使運營商在由2G向3G低風險平滑過渡過程中受益。兼具2G系統的低成本和3G系統得到初步應用的需求,激勵著基站設備制造商采用新的可重構硬件平臺。許多BTS制造商都認為多載波收發機是可支持無線空中接口標準的單一底層基礎設計解決方法。

傳統的基站架構要求對所處理的每個RF載波(數字和模擬系統各為4到80個信道)都有一個完整的收發機。這類無線信號必須進行多路分集。多載波收發機的妙處在于通過天線完成每個RF載波的數字域處理,消除無線冗余,從而得到單一的高性能無線頻率。

基于TD-SCDMA無線傳輸技術的無線接入網(RAN)可以與GSM的核心系統進行連接,實現3G業務及功能在現行GSM網絡上的無縫集成。這將使GSM運營商以成本效益的方式向3G升級,因為GSM核心網絡設施的完全集成和重用成本對3G的經濟性起著關鍵作用。

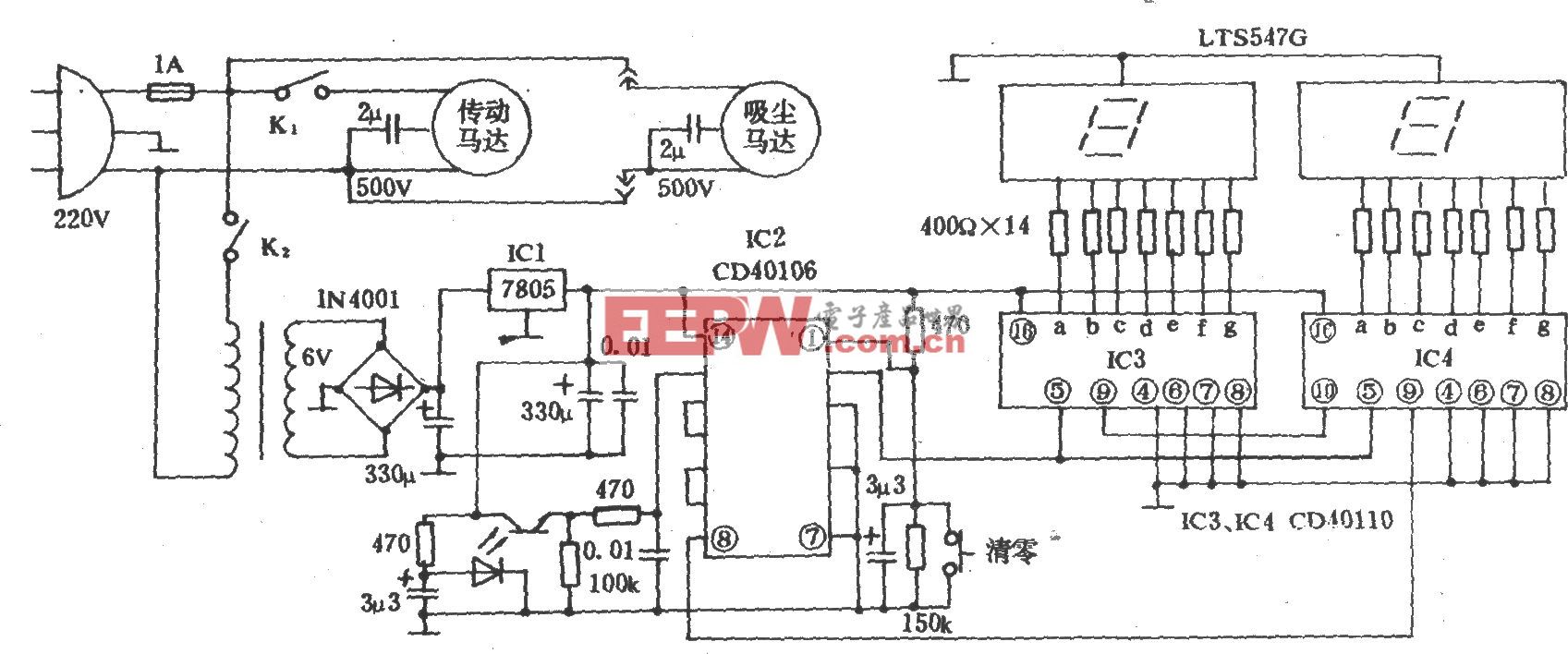

圖1所示是一個幀的物理結構。這個5ms幀由7個用箭頭表示上下行鏈路方向的時隙組成。TS0總是下行鏈路,TS1總是上行鏈路。與通常的表示法相反,可以看到時隙的凈長度不含鄰近的保護時間。上行與下行鏈路間的轉換點可以設置在TS1與TS2以及TS6與TS0之間,保護時間僅為12.5微秒。TS0之后是用于實現UE同步的下行鏈路導頻信號DwPTS。用來進行隨機存取和同步化的100微秒UpPTS由UE發送,并需落到所設定的125微秒窗口內。但它有可能在上升沿的間隙提前到達,這樣就要求BTS控制器(BTSC)盡早進入接收狀態。這種間隙偶爾也用于校準用途。

TD-SCDMA無線接口與3GPP集成,可作為UTRA-TDD、UTRA-TDD LCR的低芯片速率選擇方案。UTRA-TDD HCR使用高芯片速率模式(芯片速率3.84Mchips/s,帶寬5MHz)。符號時間Ts=Q/Tc,Tc=1/芯片速率=0.78125s,符號時間Ts取決于擴展系數Q。調制方式采用QPSK。對Tx的每一芯片進行脈沖波形濾波。脈沖波形濾波器的沖激響應h(t)應為

(1)

其中a=0.22。

數模轉換器(DAC)和多載波功率放大器(MCPA)必須保護幾個以數字方式產生的載波頻譜不對相鄰信道造成訛誤或寄生信號。基站Tx在各個載波上進行載波間互調(IM)的結果,產生的頻譜再生必須最小。DAC用來產生更高的頻率,使上變頻級數由2個減為1個。不利的方面是轉換器性能在較高的頻率下會變差。多載波傳輸與單載波無線方案不同,后者借助模擬濾波器去除可造成相鄰信道訛誤的無用信號。而多載波架構在整個傳輸帶寬范圍內限制失真。

當RF PA承載不具有固定包絡、一組載波或數個CDMA組合信號的信號時,PA便產生IM失真(IMD)。由于IM功率作為干擾流入相鄰信道,因此,高級的寬帶PA線性化策略已成為多載波收發器的關鍵技術。

按照3GPP標準要求,TD-SCDMA TX的設計應實現TD-SCDMA BTS與GSM及DCS-1800BTS的共存。為降低對MCPA的線性度要求,DAC的相鄰信道泄漏比(ACLR)規范應不超過表1的規定值。

TD-SCDMA信號的峰值與均值功率比(PAPR)取決于編碼和載波數。所有的編碼和載波作同相相加時,RAPR的值最大。

AD6623是一種四信道104M樣值/s傳輸信號處理器(TSP),適合多模無線基站Tx架構。它用于基站Tx的DSP與高速DAC之間。16位DAC的動態范圍允許多個AD6623組合信道在具有高PAPR值的數兆赫帶寬上傳輸,平均輸出信號電平為全量程范圍的一定比例。此外,可編程系數有限沖激響應(FIR)濾波器級允許將反成像(anti imaging)和靜態均衡功能結合到一個單一的具有成本效益的濾波器中。可編程功率上升/下降單元對基于TD-SCDMA所規定的時隙上的功率延升提供支持。

每個級聯集成梳狀(CIC)濾波器級的內插因子范圍和二級CIC濾波器中的重復取樣器,使AD6623能有效地以高速樣束生成窄帶和寬帶載波。高分辯率數控振蕩器(NCO)支持頻率規劃的靈活運用。該高速NCO能夠將正交的采樣信號調整到中頻(IF)信道,或者NCO直接在IF信道進行頻率調制。

AD9777是用于基帶或IF波形重建的16位高性能可編程2x/4x/8x內插Tx數據轉換器(TxDAC),要求動態范圍要高。AD9777特有的串行接口(SPI)具有高度可編程性,可支持以下增強型系統級選件,包括:

* 2x/4x/8x內插濾波器可選;

* 帶鏡像抑制的Fs/2、Fs/4或Fs/8(Fs:AD9777的采樣頻率)數字式正交調制方式;

* 直接IF模式,可編程信道增益與偏移控制。

AD8346是用于0.8-2.5GHz的半導體射頻集成電路同相/正交(I/Q)調制器。其相位精度和幅度平衡性能允許對RF進行高性能直接調制。

這種Tx子系統可采用模擬器件公司(ADI)的ADSP TS001M Tiger-SHARC DSP進行補償。該DSP適于200MHz下每秒20億次16位乘法/累加運算的通信應用。

TD-SCDMA芯片速率低于400MHz以下的最高整數過采樣率為399.36MHz(1.28×39×8.0Mchips/s)。AD6623濾波器對輸出信號帶寬進行約束,使之保持低于TD-SCDMA所規定的傳輸掩膜要求。基帶信號的芯片速率為1.28Mchips/s。運行于fclk=99.84MHz下的數字上變頻器進行升余弦濾波、內插和頻移處理。多達3個TD-SCDMA載波可放置在20MHz的頻寬內。串行數據源由AD6623處理信道以fsclk=fclk/2=40.96Mb/s (或1.28×32.00=40.96Mb/s)的速率驅動數據。這基本上是AD6623的理想結構。主控時鐘以99.84MHz運行,使可編程FIR濾波器對39個抽頭進行計算。

(2)

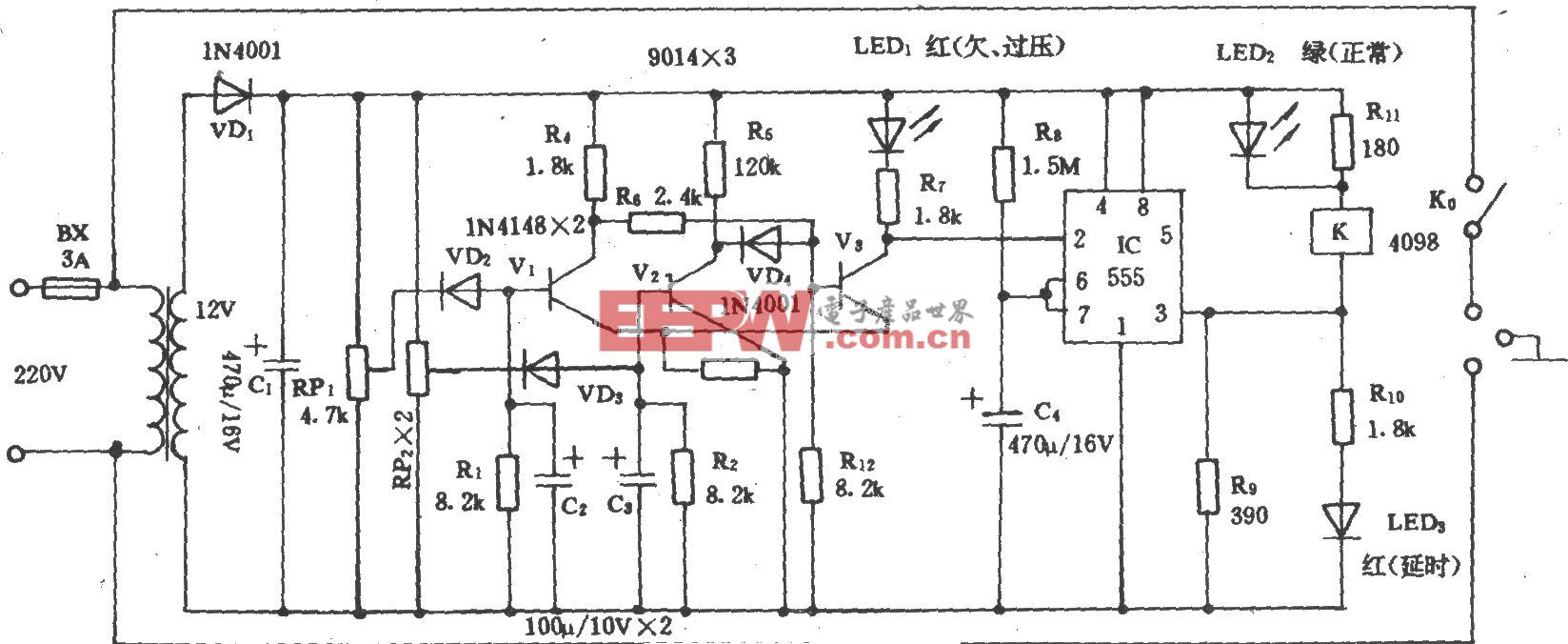

可編程系數FIR濾波器在通帶內以因數3內插輸入信號并對CIC濾波器的滾降特性進行預補償。RAM系數(RCF)輸出速率為每處理信道3.84M樣值/s。第二濾波器級--5階CIC(CIC5)濾波器的內插為Lcic5=13。CIC5的輸出速率為49.92M樣值/s。第三濾波器級-2階重采樣CIC無任何內插(LrCIC2=1)。CIC2的輸出速率為49.92M樣值/s(綜合樣率)。CIC和NCO以49.92MHz的綜合速率運行實現功率節省。內插的TD-SCDMA信號經NCO產生的正弦/余弦序列上變頻到IF=-6.24MHz。載波經AD6623變換到-16.24MHz到3.76MHz的頻帶范圍內。圖2示出AD6623的復合變換功能,通帶紋波0.116dB,阻帶頻率0.87MHz。

所有濾波器的預期誤差矢量幅度(EVM)必須小于2%。EVM通過觀察與升余弦(RRC)接收濾波器相匹配的實際AD6623濾波器的時域沖激響應而計算得出。由于合適的RRC存在無限響應,因此,使用了大量符號,以避免由傅立葉變換造成的誤差矢量嚴重混淆,導致不精確的量度。這一點可以通過觀察沖激響應曲線中心的小數值結果得到驗證。計算所得的EVMrms為0.47%。

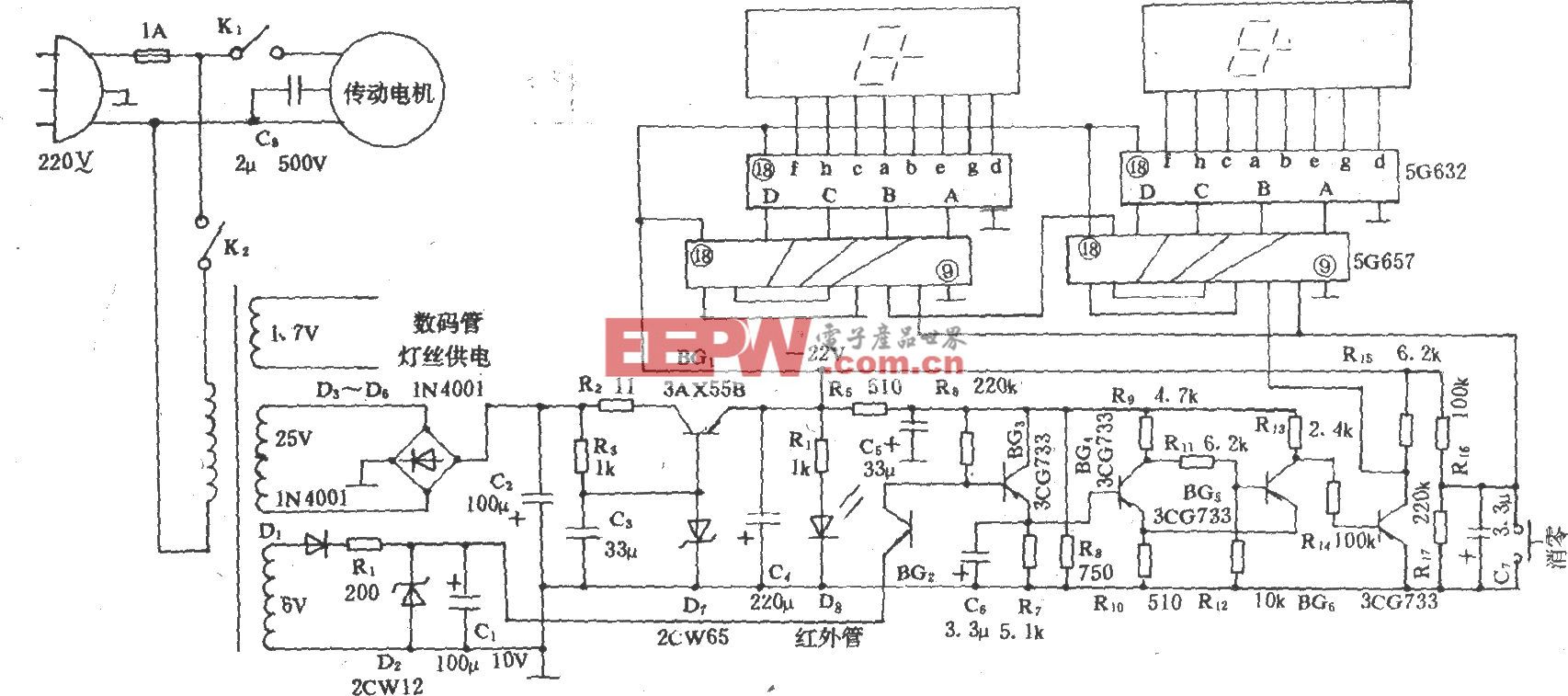

AD9777接受來自AD6623的交織I/Q數據(圖3)。數據接口為32位寬,實部16位、虛部16位。AD9777用其雙DAC產生綜合調制IF信號,該信號通過模擬正交調制器變換為RF信號。DAC的鏡像抑制和頻率偏移性能決定了其后模擬濾波器級的要求。AD9777在LDAC=8、相應采樣率為399.36M樣值/s條件下內插數據。如此配置可使43抽頭的第一級濾波器在399.36/8=49.92MHz的頻率下工作。TD-SCDMA載波覆蓋33.68MHz-53.68MHz頻段。中心頻率為IF 43.69MHz(49.92x7/8MHz)。從圖4所示的矩形區域中,可以確定AD9777的輸出端有3個經濾波的TD-SCDMA載波。

位于AD9777之后的正交調制器有兩個以正交方式工作的混頻器。混頻器的輸出按照頻率元件的相位關系和符號進行內部求和,以執行數學運算。■ (承慧譯)

參考文獻:

1. “TD-SCDMA的優勢和實現方法”,2000年國際通信技術會議錄 WCC-ICCT2000

2. “TD-SCDMA系統的智能天線性能”,2000年國際通信技術會議錄 WCC-ICCT2000

3. “物理通道與基于物理通道的傳輸通道”,1999年10月TS C102

4. “高速寬帶DAC實現多載波蜂窩基站”,《Electronic Design》2000年12月18日

圖1 用箭頭表示上下行鏈路方向由7個時隙組成的5ms幀

圖1 用箭頭表示上下行鏈路方向由7個時隙組成的5ms幀

圖2 AD6623對濾波后TD-SCDMA載波的頻率響應

圖3 三載波TD-SCDMA Tx方框圖 圖4在矩形區域內可確定AD9777輸出端有3個經濾波的TD-SCDMA載波

圖4在矩形區域內可確定AD9777輸出端有3個經濾波的TD-SCDMA載波

評論