基于SoPC的狀態監測裝置的嵌入式軟硬件協同設計

2.2 信號分析IP設計

為節約CPU資源,減輕軟件開發負擔,本系統中信號分析采用FPGA硬件邏輯完成,信號分析IP直接從原始信號數據計算得到直流,基波以及各次諧波的幅值和相位等特征量,具有運算時間固定,速度快,不易出錯,不占用CPU軟件資源等優點。設計框圖如圖2所示。主要包括數據流控制邏輯,FFT運算IP,幅頻相頻計算模塊,均值和峰峰值計算模塊,分析結果存儲緩沖RAM,PLB_EMC接口伺服邏輯。本文引用地址:http://www.j9360.com/article/148140.htm

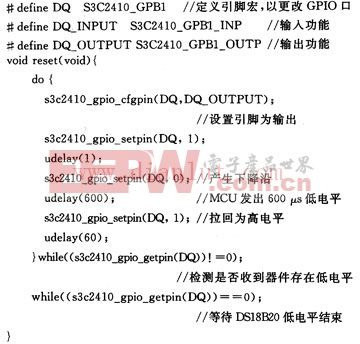

其中FFT運算和幅值相位計算采用了Xilinx的IP,為節省FPGA邏輯資源,4 096點FFT采用基-2(Radix-2)算法簡化版,突發輸入輸出模式,在速度達到的情況下盡可能的縮減面積。

在完成了信號分析IP的邏輯后,進行了仿真工作,仿真數據由Matlab模擬計算得到,通過TestBench送給分析模塊進行仿真,仿真環境為Mentor Graphics公司的ModelSim 6.3g。下面是一些具體的仿真結果以及和Matlab仿真的對比。

在Matlab中產生一個正弦信號,并做4 096點FFT,計算結果如圖2所示。

圖3是FFT工作的時序圖,可以看到在選擇了基-2(Radix-2)算法簡化版,突發輸入輸出模式后,4 096點FFT的計算時間為533.24 μs,較軟件算法快很多,從而使系統能勝任大數據量(84路16位數據)高分辨率(4 096點)信號分析。

圖2和圖3是對模擬數據進行Matlab仿真和ModelSim仿真二者結果的比較,可以看到原始計算結果有一定的誤差,歸一化后完全一致,產生誤差的主要原因是在Matlab中的FFT是浮點數計算,而在FPGA中的FFT選擇的是定點數計算。仿真結果表明此模塊可以完成信號分析的功能,且分析結果達到較高精度。

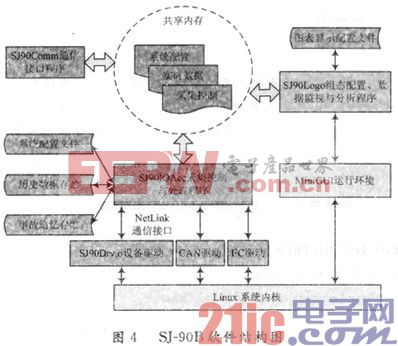

3 裝置軟件設計

裝置的軟件結構如圖4所示,主要由以下幾個部分組成:嵌入式Linux操作系統、設備驅動程序(SJ90Dry.o)、數據采集控制與處理程序(SJ90IOAcc)、系統組態配置與監視分析程序(SJ90Logo)、通信接口程序(SJ90Comm)、CAN網驅動和I2C驅動。

其中:

(1)嵌入式Linux操作系統:主要負責進程管理、進程間通信、內存管理、實現文件系統、提供I/O接口及對其他資源進行管理;

(2)設備驅動程序(SJ90Dry.o):運行于系統內核空間,將緩存的存貯空間映射為字符設備,響應設備中斷,建立采集數據交換緩沖存貯,提供用戶程序與操作系統的接口,完成用戶空間和內核空間的數據交換;

(3)數據采集控翻與處理程序(SJ90IOAcc):主要負責建立共享內存,管理系統配置信息,實時數據,提供連續、自主的在線數據采集控制、信號處理、報警檢測、歷史數據存貯和故障錄波存貯等功能,通過設備讀寫和NetLink通信接口與內核態設備驅動程序進行數據交換;

(4)系統組態配置與監視分析程序(SJ90Logo):基于MiniGUI圖形環境,提供可視化的系統參數配置(含機組、傳感器、通道、測點信息配置等)功能,提供多種實時數據監視圖表、歷史趨勢分析圖表和時頻振擺分析圖表;

(5)數據通信接口程序(SJ90Comm):實現本系統與其他系統的數據交換,系統提供串口和網絡2種方式傳送數據,支持的協議分別為MODB US_RTU和MODBUS_TCP;

(6)CAN網驅動和I2C驅動:運行于系統內核空間,提供用戶程序與操作系統的接口,完成用戶空間和內核空間的數據交換;CAN網驅動獲取開關量以及慢變量信號;I2C驅動完成硬件點燈以及報警等功能。

4 結語

基于SoPC的軟硬件協同設計在圖像處理、無線通信、軍事武器等場合已經有了較多應用,本文則將該設計方法應用于狀態監測裝置中,并通過該設計方法最大限度地提升和優化了該采集系統的性能。筆者認為該設計方法同樣適合于電力行業中其他一些實時性強、運算量大、功能復雜的多路采集分析裝置中,以該設計思路替代以往的CPU+DSP,CPU+FPGA等多處理器芯片的設計方法,可實現系統級優化設計。

評論