FAE講堂:利用賽靈思FGPA實現降采樣FIR濾波器

多級方法

本文引用地址:http://www.j9360.com/article/119299.htmFIR-Complier已經為這種多相L/M=6/25濾波器生成了非常小的內核。不過,我們需要再次采用多級方法,因為這種方

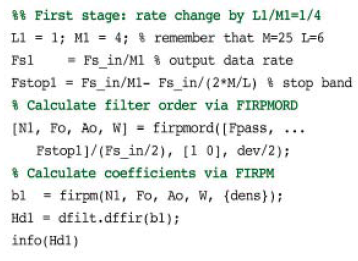

法使我們能夠進一步節約DSP48與BRAM。在手動設計多級系統時, 如本例所示,所有濾波級都必須采用與參考濾波器相同的通帶頻率 (Fpass)。

各級通帶紋波均相等,是由參考濾波器通帶紋波除以級數算出。各級的差異是阻帶頻率。第一級無需在Fstop截止,因

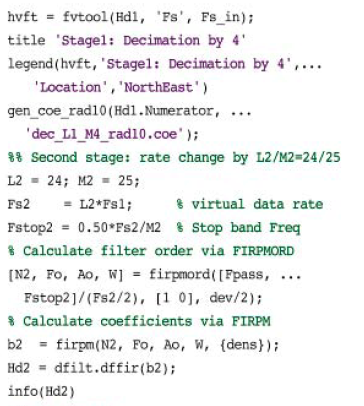

為轉換帶寬會變得太急促(太多系數);現實中我們所需要的只是讓第一級在Fstop1=Fs_in/M1- Fs_in/(2M/L)截止。實際上Fs_in/M1與其所有倍數此時都是放置所有復本的新采樣頻率,而Fs_in/(2*M1)是Fs_in/M1中第一個復本的帶寬的一半。以下是相關MATLAB代碼。

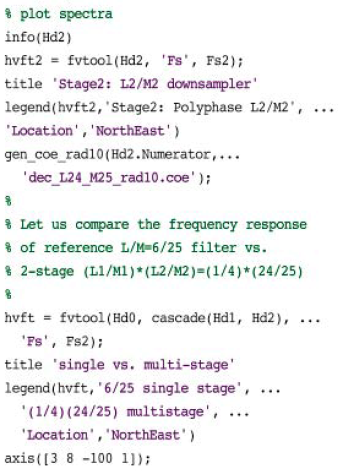

由于第一級是M1=4整數降采樣器, 因此其FIRCompiler GUI設置與圖1所示非常相似。唯一不同的參數是COE文件名(即dec_L1_M4_rad10.coe)、抽取率值(M1=4)、輸入采樣頻率 (50 MHz) 和時鐘頻率 (150 MHz)。另一方面,第二級采用 L2/M2=24/25 有理數速率變化,因此,FIR-Compiler設置與圖6所示大同小異。此處COE文件名為dec_L24_M25_rad10.coe,插值速率值設為L2=24,而輸入采樣頻率為12.5 MHz。

在布局布線之后,上述兩個濾波級占用以下FPGA資源:

第一級(L1/M1= 1/4):

Slice 觸發器數量:321 個

Slice LUT數量:223 個

占用 Slice數量:62 個

DSP48 MAC單元數量:4 個

BRAM單元數量:0 個

第二級(L2/M2 = 24/25):

Slice觸發器數量:206 個

Slice LUT數量:209 個

占用 Slice數量:68 個

DSP48 MAC單元數量:3 個

BRAM單元數量:1 個

由于采用多級方法,與單級理想濾波器資源占用相比,我們現在可以節約 3% 左右的觸發器,4%的LUT,15%的Slice,46%的DSP48以及83%的BRAM單元。尤其是我們只需少得多的MAC與BRAM單元,分別只有6個和5個。原因是第二個濾波器以更低的輸入采樣頻率運行,而采用整數速率變化的第一個濾波器可以充分利用系數對稱。

其它資源

我們在本輔導資料中介紹了兩個降采樣濾波器例子,一個是整數系數(50),另一個是有理數系數(25/6),而且

本文強調了在MATLAB設計濾波器以及采用FIR-Compiler和CIC-Compiler 在賽靈思FGPA中實現它們的方法。相關數據手冊詳細介紹采用CORE Generator實現濾波器所涉及的參數設置。

如果有興趣進一步深入DSP領域,有兩本專著具體介紹諸多理論和相關 MATLAB 指令:《數字信號處理基礎與應

用》,作者:Li Tan(Elsevier,2007 年)和《通信系統多速率信號處理》,作者:Fredric J. Harris(Prentice Hall,2004年)。另外,賽靈思網站提供大量有關多速率數字上變頻和下變頻的應用手冊(尤其是 Xapp113、569、1018 與 936)。

最后,為了理解如何有效實現DSP算法,本人強烈推薦參加賽靈思培訓課程《賽靈思FPGA的DSP實現技巧》。

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

電源濾波器相關文章:電源濾波器原理

評論