ST NAND閃存數據吞吐量創造世界記錄

——

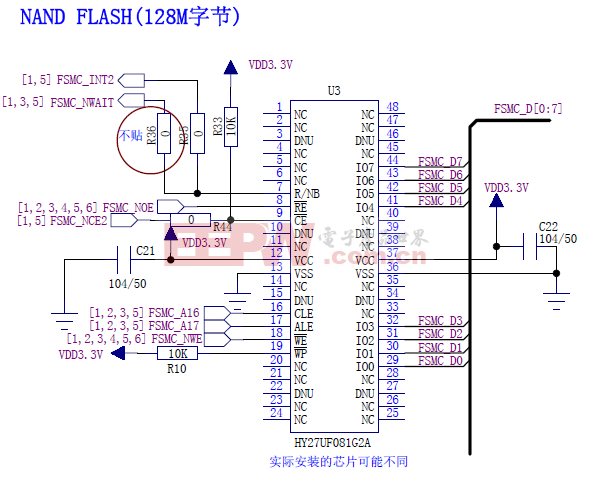

意法半導體公布了數據吞吐量創世界記錄的4Gigabit NAND閃存的技術細節,ST新閃存芯片的數據吞吐量高達36MB/s, 比今天市場上的最好成績還高大約50%。 新芯片內嵌一個功能強大的糾錯處理器,每頁可以改正最多五個錯誤,為高度可靠性和高速數據傳輸提供了保證,同時還簡化了存儲系統的設計,在舊金山國際固態電路大會(ISSCC) 上,意法半導體和韓國現代海力士(Hynix)的研究人員合創的論文將對新芯片給予詳細介紹。

高密度NAND閃存是新興的便攜海量存儲設備如USB密鑰和MP3播放器的關鍵組件。 這個市場的特點是存儲容量越高越好,每位成本越低越好,這種需求正在日益提高。 因每個存儲單元可以存放兩位或多位數據,多級單元閃存 (MLC)技術在密度和成本方面比單位單元(SBC)NAND閃存技術占有明顯優勢,但是在數據保存和擦寫循環性能方面占劣勢。 因此,MLC NAND閃存通常需要更復雜的糾錯碼(ECC)電路,SBC和MLC NAND閃存現行的糾錯方法都是通過系統處理器執行糾錯算法。不過,在這些應用中,執行系統處理器功能的處理器通常沒有專用的模數指令來更好地執行這些算法,結果導致閃存的吞吐量通常只有幾兆字節/秒。

ST的閃存芯片采用一種完全不同的解決方法:在芯片上嵌入一個復雜的糾錯代碼(ECC)處理器。這個專用的處理器執行高效的著名的糾錯技術BCH (Bose-Chaudhuri-Hocquenghem) ,BCH算法被廣泛用于WLAN以及其它的需要可靠地檢測糾正多個數據傳輸錯誤的應用場合。 此外,嵌入式ECC處理器采用一個創新的體系結構,針對面向字節的串行讀取存儲應用(如MPC3播放器和USB密鑰)優化了ECC的計算性能,最大限度地縮減了硅的占用面積、延遲時間和功耗。 結果,ST的新閃存芯片讀取速率達到了36MB/s, 遠遠高于市場以前報道的糾錯前23MB的讀取速率。

“這項創新的突破技術將很快成為ST每位兩單元NAND閃存的開發計劃的標準,” ST NAND閃存產品部總經理Carla Golla表示, “此外,我們預計這種方法會成為每單元兩位閃存的行業標準,目前這類產品正在擴大在NAND閃存市場的占有率。這種方法實現了多級單元技術的優勢,同時沒有犧牲系統讀取速率和可靠性。”

這項技術是在意法半導體Agrate非易失性存儲器制造廠開發的,新產品破了吞吐量的世界記錄,但沒有耗用過多的硅面積、功耗和延遲。 ECC電路占芯片面積僅1.3mm2,不到芯片總面積的1%,芯片平均耗電小于1mA。 糾錯電路也分割成不同的功能模塊,以便在檢測到錯誤時把糾錯時間壓縮到最小。新產品配置兩個獨立的糾錯模塊,一個用于糾正2-5個錯誤,用時250µs,另一個用于糾正單一的錯誤,用時僅 34µs。 因此,嵌入式ECC是硅面積與延遲兩個特性之間的一個優化折中方案。

評論